Protected: ACLR Simulation in Cadence

There is no excerpt because this is a protected post.

Ideal Blocks in Cadence

Ideal Blocks in Cadence Time to time, debugging or modelling a circuit, we look for ideal blocks in Cadence that can do the job, prove the concept before you go on fully developing the thing. We heard you. Here are some ideal blocks that are already available in Cadence Virtuoso libraries that you can get […]

Print Noise Summary to a File in Cadence

Print Noise Summary to a File in Cadence When netlist of your circuit is too big, printing noise often crashes Cadence and it gets too slow in loading results, going to print window etc. Instead, we can just directly print noise summary to a file without needing to go to maestro itself. Here is how […]

Cadence Tips and Tricks

Cadence Tips & Tricks Stop wasting time on manual work. Use these Cadence tips & tricks to automate repetitive tasks, increase work efficiency and rather spend your saved time on doing something creative. 1. Wrap your Corners Make a wrapper file for different corner cases to prevent yourself from inflicting the pain of different model […]

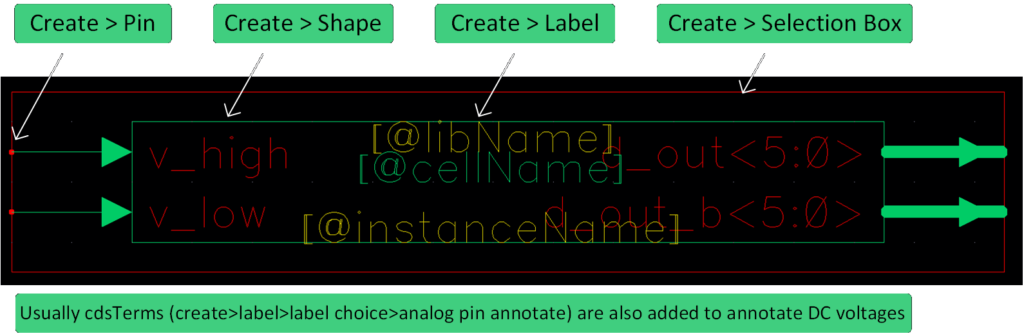

Decimal to Binary Decoder in Cadence using Verilog

Guide on how to design decimal to binary decoder in Cadence from symbol to verilog to schematic test.

Ideal Low Pass Filter in Cadence

Ideal Low Pass Filter in Cadence Are you running FFT on time domain signal and need to have a brick-wall low pass filter to remove aliasing? Are you debugging non-linearities like IM3 and want to filter out certain harmonics to see what were their contribution? You need reconfigurable ideal filters. These are top three options […]

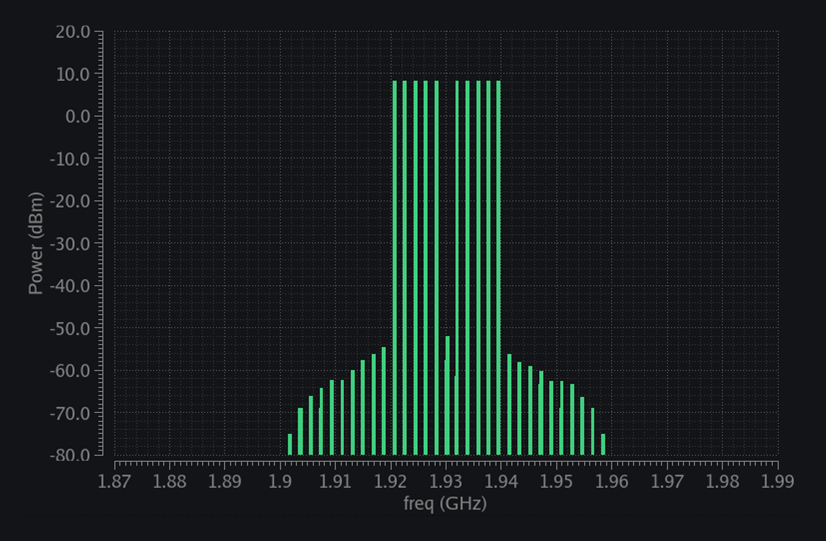

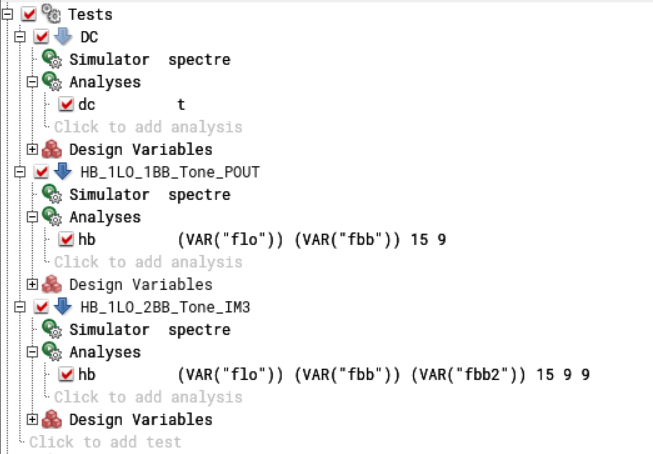

Transient to Spectrum

Transient to Spectrum In IC design, there comes a time when netlist of a circuit gets too big that harmonic balance (HB) or periodic steady state (PSS) simulations just would not converge or take eternity to finish. It is then we resort to classic time domain transient (tran) simulation where convergence is almost always guaranteed […]